Also, I need to finish re-testing the skeleton C code and add the serial test code to it.

David said he might drop by at some point this afternoon with his parents so that they could see the lab. He said he would text first though. - They came by and we chatted for a while. His Dad suggested we use a dremel tool to file down the pin edges on the SMA edge connector. Ray said we might have one upstairs in the physical electronics lab. However, we went upstairs and couldn't find it - he might have misremembered. We could requisition a new one, or perhaps just some new parts.

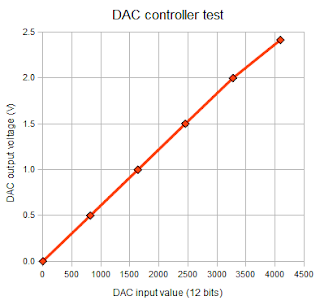

After David left, I finished updating the code to take 8 system clock cycles instead of 6 per bit-clock in the DAC output stream, and re-tested the levels. It worked! The new values are: 2.4155, 1.9996, 1.5017, 0.9991, 0.4994, 0.0004. I.e., all but the first are correct to within <1% (<10 mV), and the first one is only off by 100 mV because +2.5V instead of +2.7V is supplied to the DACs, which we already knew was a problem. Ray says that's fine, because we can add an analog inverter, so that our thresholds will be at the low end of the scale, instead of the high end.

Here's a graph of the data... Nice and linear, aside from the slight expected slumping at the high end. Note also all points but the last one fall squarely on the multiples of 0.5V, as expected.

I tried integrating the latest code into my new, slimmed-down project with the Nios system, but I am having some weird problems:

- When I try to download the ELF from the Nios II IDE into the Nios system, it is failing verification and won't proceed with the run.

- When the design is loaded, the COSMICi banner appears on the JTAG STDOUT (viewed in nios2-terminal), and the test pulse sequence appears as expected at first, but...

- The digitized output data was missing on some of my test runs (but not others);

- The DAC levels are initially wrong (way off)... but then,

- After just a minute, the following things all happen at about the same time:

- The sequence of test pulses halts;

- The DAC level goes to the CORRECT value (?!?!?)

- An I/O error on JTAG UART causes nios2-terminal to exit. (Sometimes after outputting a sequence of bad characters first.)

No comments:

Post a Comment